# Design D Flip-Flop for Low Power Application

# Kumar Vinayak, Owais Ahmad

Abstract: Power consumption is a major problem of system performance and it is listed as one of the top three challenges in International Technology for Semiconductor. In practice, a large portion of the on chip power is consumed by the clock system which is made of the clock distribution network and flip-flops. In this thesis, various design techniques for a low power clocking system are surveyed. Among them minimizing a number of clocked transistor is an effective way to reduce capacity of the clock load. To approach this, we propose a conditional data mapping technique which reduces the number of local clocked transistors.

Keywords: Flip Flop, Low Power, CMOS Circuit

#### INTRODUCTION

# PROPOSED WORK

# 1.1 Theoretical design procedure

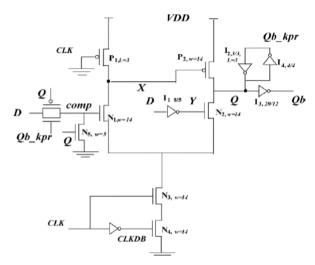

This chapter will discuss on a proposed new clocked pair shared d flip-flop design The proposed work aims to study the various possible methods of CPSDFF and to assess the low power consumption various techniques. In the present work, .In contrast, flip-flop (CPSDFF), reduction in the number of clocked transistors the objective to reduce clocked load our study CDFF and CCFF use many clocked transistors, CDMFF reduces the number of clocked transistors but it has redundant clocking as well as a floating node. To ensure efficient and robust implementation of low power sequential element, we propose CPSDFF (fig 1.1) to use less clocked transistor than CDMFF and over-come the floating problem in CDMFF

# 1.2 Circuit description

In this circuit of clocked-pair-shared flip-flop, a clocked pair (N3, N4) is shared by first and second stage of the latching part as which is shown in figure 1.1 clocked loads which is used in CDMFF, it result in about 40% reduction in number of clocked loads. Additional to this the internal node X is connected to supply voltage Vdd with the help of a pseudo NMOS P1, so is not floating point is now present, and result also shows an improvement in the noise robustness of node X.

When input D stays at HIGH level then Q=1, here N5 is kept ON, N1 will be kept off to avoid the redundant transient activity at node X, as well as in any short circuit current. PMOS P2 is allowed to pull Q to high level when D switches to 1 value. Then second NMOS branch (N2) is in charge for pulling down the output of Q if D = LOW value and Y=1 when the clock pulse is arrives. PMOS present in N1 should turn on NMOS N2 when D=LOW.

# Revised Version Manuscript Received on June 27, 2016.

Kumar Vinayak, MTech Scholar, Department of VLSI, Noida International University, Noida (U.P.), India

Owais Ahmad, Assistant Professor, Department of VLSI, Noida International University, Noida (U.P.), India

Figure 1.1 Diagram of CPSDFF

Although P1 is always ON, short circuit only occurs one time when D makes a transition from LOW to HIGH, and then discharge path is disconnected after two gates delay. After all that, if at this time also D remains at HIGH, then the discharge path is already disconnected by N1: there would be no short circuit. Here the clocked-pseudo-NMOS scheme is different from the general idea of common pseudo-NMOS logic. In the previous one we use clocked transistors in the pull down branch. P1, N1, N3, and N4 should be properly scaled to guarantee a correct noise margin. CPSFF uses three less clocked loads, which by default leads to about 40% reduction in number of clocked loads. It achieves 25% less clock driving consumption than CDMFF, which improves efficiency.

#### II. **METHODOLOGY**

#### Surveyed technique for reducing clock 1.1.

Most of the flip-flops presented here are dynamic in nature. and some internal nodes are precharged and evaluated in each cycle without producing any useful activity at the output when the input is stable. Reducing this redundant switching activity has a profound effect in reducing the power dissipation, and in the literature many techniques were presented for this purpose. A brief survey of such techniques is conducted in this work, and the main techniques were classified as follows: Reducing Capacity of Clock Load: 80% of non clocked nodes have switching activity less than 0.1. This means reducing power of clocked nodes is important since clocked node has 100% activity. One effective way of low power design for clocking system is to reduce clock capacity load by minimizing number of clocked transistor. Any local clock load reduction will also decrease the global power consumption. This method reduces power by decreasing

clock capacity in equation.

# **Design D Flip-Flop for Low Power Application**

In my project I am making a comparison (power) with the existing flip flop and find out that the new flip flop reduces the power. CPSDFF use less clocked transistor than CDMFF, CDFF&CCFF overcome the floating problem.

#### Advantages

- > CPSDFF uses less clocked Transistors

- Less power & Area

- very less clock delay

# III. RESULT AND DISCUSSION

### 3.1. Simulation results of proposed CPSDFF

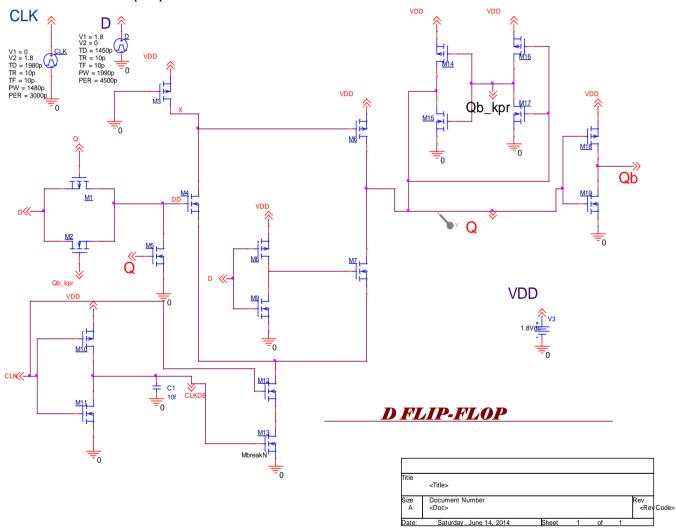

All the simulation results which include sizing of transistors, power consumption and timing metrics are obtained and discussed in this chapter The performance of the proposed CPSDFF was verified using the PSpice simulation program The simulation results flip flop were obtained from P-SPICE

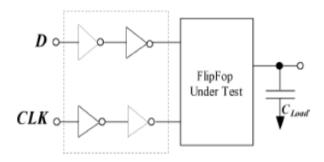

simulation in 0.18µm CMOS technology at temperature, the supply voltage is 1.8v. The aspect ratio of the transistor are given in Table 2.1.The parasitic capacitances were extracted from the layouts. The setup used in our simulation is shown in Fig.2.1-In order to obtain accurate results .we have simulated the circuits in a real environment, where the flip flop inputs(clock, data) are driven by the buffers, and the output is required to drive an output load. An inventor is placed after output Q, providing Protection from direct noise coupling. The value of the capacitance load at  $Q_b$  is 10fF, which is selected to simulation a fan out of 14 minimum sized invertors (FO14). A clock frequency of 111MHz is used. The results of the CDMFF circuit show 10.276µW power dissipation. Flip flop with reduced number of transistor for low power &high performance

Fig 2.1:- PSPICE capture of CPSDFF

Table 2.1 Aspect ratios of the transistors CPSDFF

A test bench is setup to compare the performance of all flip-flops as shown in Figure

| Transistor      | W(µm) | L(µm) |

|-----------------|-------|-------|

| M1,M2,,M4       | 2.25  | 0.18  |

| M3              | 5     | 3     |

| M5              | 0.9   | 0.18  |

| M6,M7,M12,M13   | 2.52  | 0.18  |

| M8,M9           | 8     | 5     |

| M10,M11,M14,M15 | 3     | 3     |

| M16,M17         | 4     | 4     |

| M18,M19         | 20    | 12    |

|                 |       |       |

Fig 2.2 Setup used for flip flop simulation the Input are driven by the inverters, and output is driving a capacity load of14 minimum inverters(FO14)

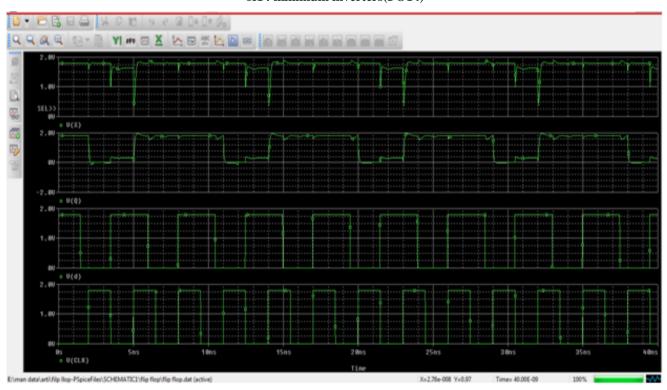

Figure 2.3:-Simulation result of CPSDSFF

Fig 2.3 shows the output voltage with respect to clock in work on D flip flop while X and Y terminal are terminated with 2.0v to 40 ns

# **Design D Flip-Flop for Low Power Application**

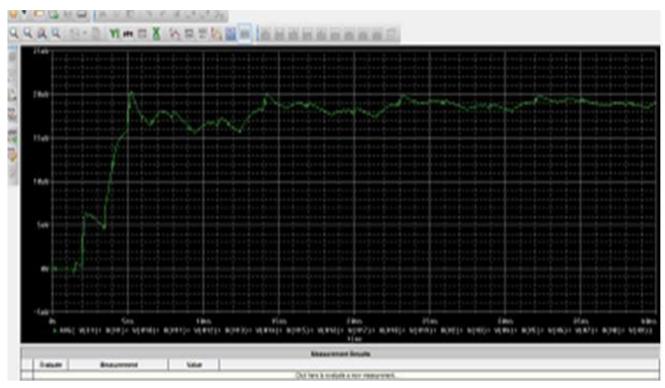

Fig2.4:- Waveform for Power Consumption at process

Fig 2.4 shows the Average power dissipation with respect to time in work on D flip flop while X and Y terminal are terminated with 20uw to 40 ns respectively. The total power dissipation is 10.276µ watts.

# Comparison of Total Power dissipation table:-

| TYPE   | NO of Transistor | No of Clocked | Power Consumption |

|--------|------------------|---------------|-------------------|

| CDMFF  | 22               | 7             | 11.253μw          |

| CPSDFF | 14               | 4             | 10.276μw          |

The results of the CPSDFF circuit show 10.276 W power dissipation. Flip flop with reduced number of transistor & reduction in size by reducing the number of clocked load for low power &high performance.

#### IV. CONCLUSION

In this project, a variety of design techniques for low power clocking system are reviewed. One effective method, reducing capacity of the clock load by minimizing number of clocked transistor, is elaborated. Following the approach, one novel CPSDFF is proposed, which reduces local clock transistor number by about 40%. In view of power consumption of clock driver, the new CPSDFF outperforms prior arts in flip-flop design by about 24%. In general, low power design for combinational and sequential circuits is an important field and gaining more importance as time goes by and will stay an important area of research for a long time. We have presented a survey and evaluation of lowpower flip-flop circuits. Our experimental results enabled us to identify the power and performance trade-offs of the flipflop design. The simulation environment is setup with a supply voltage of 1.8V, temperature, clock frequency of 111 MHz and a capacitive load of 10fF.

# REFERENCES

B. Kong, S. Kim, and Y. Jun, "Conditional-capture flip-flop for statistical power reduction," IEEE J. Solid-State Circuits, vol. 36, no. 8, pp. 1263–1271, Aug. 2001.

- C. L. KimandS.Kang, "A low-swing clock double edge-triggered flipflop," IEEEJ. Solid- State Circuits, vol.37, no.5, pp.648–652, May2002.

- P. Zhao, T. Darwish, and M. Bayoumi, "High-performance and low power conditional discharge flip-flop," IEEE Trans. Very Large Integr. (VLSI) Syst., vol. 12, no. 5, pp. 477–484, May 2004.

- Kong Teh, Mototsugu Hamada, Tetsuya Fujita, Hiroyuki Hara, Nobuyuki Ikumi, and Yukihito Oowaki"Conditional Data Mapping Flip-Flops for Low-Powerand High- Performance Systems" IEEE transactions on very large scale integration (vlsi) system vol. 14, no. 12. december 2006.

- B. S. Kong, S.-S. Kim, and Y.-H. Jun Peiyi Zhao, Jason McNeely, WeidongKuang, and "Design of Sequential Elements for Low PowerClocking System" IEEE Transaction May 2011.

- A Survey on Sequential Elements for Low Power Clocking System" Journal of Computer Applications ISSN:, Volume-5, Issue EICA2012-3, feb 10, 2012.

- Seyed E. Esmaeili, Asim J. Al-Kahlili, and Glenn E. R. Cowan"Low-Swing Differential Conditional Capturing Flip-Flop for LC Resonant Clock Distributio Networks" IEEE transactions on very large scale integration (vlsi) systems, vol. 20,no. 8, august 2012.

- N. Nedovic, W. W. Walker, and V. G. Oklobdzija, "A test circuit for measurement of clocked storage element characteristics," IEEE J. Solid-State Circuits, vol. 39, no. 8, pp. 1294–1304, Aug. 2004.

- D. Markovic, B. Nikolic, and R. W. Brodersen, "Analysis and design of low-energy flip- flops," in Int. Symp. Low Power Electron. Des. Tech. Dig., 2001, pp. 52–55.

- P. Zhao, J. McNeely, S.Venigalla, G.P. Kumar, M. Bayoumi, N.Wang, and L. Downey, "Clocked-pseudo-NMOS flip-flops for level conversion in dual supply systems, IEEE Trans. Very Large Scale Integr. (VLSI) Syst., to bepublished.

- J. Tschanz, S. Narendra, Z. P. Chen, S. Borkar, M. Sachdev, and V. De, "Comparative delay and energy of single edge-triggered & dual edge triggered pulsed flip-flops for high-performance microprocessors," in Proc. ISPLED, Huntington Beach, CA, Aug 2001, pp. 207–212.

- G. Oklobdzija, V. M. Štojanovic, D. M. Markovic, and N. M. Nedovic, "High- Performance System Issues," in Digital System Clocking High-Performance and Low Power Aspects.: John Wiley & Sons, Inc., 2003, ch. 5, pp. 83-103.

- Bellaouar, "Why Low Power?," in Low-Power Digital VLSI Design: Circuits and Systems.: Kluwer Academic Publishers, 1995, ch. 1, pp. 1-12.

- Z. Peiyi, T. Darwish, and M. Bayoumi, "Low power and high speed explicit-pulsed flip- flops," in 45th Midwest Symposium on Circuits and Systems, 2002, vol. 2, no. 2,pp. 477- 480.

- and Systems, 2002, vol. 2, no. 2,pp. 477- 480.

15. H. Kawaguchi and T. Sakurai, "A reduced clock-swing flip-flop (RCSFF) for 63% power reduction," in IEEE Journal of Solid State Circuits, vol. 33, pp. 807-811, 1998.

- Vojin G. Oklobdzijia and Ram K. Krishnamurthy, "Clocked Storage Elements in Digital Systems," in High-Performance Energy-Efficient Microprocessor Design. Springer, 2006, ch. 3, pp. 57-168.

- 17. J. W. P. William J. Dally," Timing Circuits," in Digital Systems Engineering.: Cambridge University Press, 1998, ch. 12, pp.574-583.

- C. C. Yu, "Low-Power Double Edge-Triggered Flip-Flop Circuit Design," in International Conference on Innovative Computing Information and Control, 2008, pp. 566-566.

- Stojanovic and V. G. Oklobdzija, "Comparative analysis of masterslave latches and flip-flops for high-performance and low-power systems," IEEE Journal of Solid-State Circuits, vol. 34, pp. 536-548, 1999

- C.-C. Wang, G.-N. Sung, M.-K. Chang, and Y.-Y. Shen, "Energy-Efficient Double-Edge Triggered Flip-Flop," in Journal of Signal Processing Systems, vol. 61, pp. 347-352, 2010.

- D. F. Michael Keating, Rob Aitken, Kaijian Shi, "Introduction," in Low Power Methodology Manual For System-on-Chip Design.: Springer, 2007, ch. 1, pp. 1-12.

- V. G. Oklobdzija, V. M. Stojanovic, D. M. Markovic, and N. M. Nedovic, "Timing Energy Parameters," in Digital System Clocking High- Performance and Low Power Aspects.: John Wiley & Sons, Inc., 2003, ch. 3, pp. 47-62.

- H. Partovi, R. Burd, U. Salim, F. Weber, L. DiGregorio, and D. Draper, "Flow- through latch and edge-triggered flip-flop hybrid elements," in IEEE International Solid-State Circuits Conference, 1996, pp. 138-139.

- 24. D. H. a. H. Jackson, "High-Speed CMOS Lgic Design," in Analysis and Design of Digital Integrated Circuits in deep submicron technology.: Mc Graw Hill, 1998, ch. 6, pp. 245-270.

- J. Montanaro, R. T. Witek, K. Anne, A. J. Black, E. M. Cooper, D. W. Dobberpuhl, P M. Donahue, J. Eno, W. Hoeppner, D. Kruckemyer, T. H. Lee, P. C. M. Lin, L. Madden, D. Murray, M. H. Pearce, S. Santhanam, K. J. Snyder, R. Stehpany, and S. C. Thierauf, "A 160-MHz, 32-b, 0.5-W CMOS RISC microprocessor," in IEEE Journal of Solid-State Circuits, vol. 31, pp. 1703-1714, 1996

- B. Nikolic, V. Stojanovic, V. G. Oklobdzija, J. Wenyan, J. Chiu, and M. Leung, "Sense amplifier-based flip-flop," in Solid-State Circuits Conference, 1999 Digest of Technical Papers. ISSCC. 1999 IEEE International, 1999, pp. 282-283.

- D. DeCaro, E. Napoli, N. Petra, and A. G. M. Strollo, "A high-speed sense-amplifier based flip-flop," in Conference on Circuit Theory and Design ,2005, vol. 2,no. 2, pp.99- 102

- B. Nikolic, V. G. Oklobdzija, V. Stojanovic, J. Wenyan, C. James Kar-Shing, and M. Ming-Tak Leung, "Improved sense-amplifier-based flipflop: design and measurements," in IEEE Journal of Solid-State Circuits vol. 35, pp. 876-884, 2000.

- G. M. Strollo, D. De Caro, E. Napoli, and N. Petra, "A novel high-speed sense- amplifier-based flip-flop," in IEEE Transactions on Very Large Scale Integration(VLSI) System, vol. 13, pp. 1266-1274, 2005.

- M. Afghahi and J. Yuan, "Double-edge-triggered D-flip-flops for high-speed CMOS circuits,"in IEEE Journal of Solid-State Circuits, vol. 26, pp. 1168-1170, 1991.

- G. Aliakbar and M. Hamid, "Dual-edge triggered static pulsed flipflops," in International Conference on VLSI Design, 2005, pp. 846-849.

- 32. M. W. Phyu, W. L. Goh, and K. S. Yeo, "A low-power static dual edge-triggered flip- flop using an output-controlled discharge configuration," in IEEE International Symposium on Circuits and Systems, 2005, pp. 2429-2432 Vol. 3.

- 33. J. Tschanz, S. Narendra, C. Zhanping, S. Borkar, M. Sachdev, and D. Vivek, "Comparative delay and energy of single edge-triggered and dual edge-triggered pulsed flip-flops for high-performance microprocessors," in International Symposium on Low Power Electronics and Design, 2001, pp. 147-152.

- L. Goh Wang, S. Yeo Kiat, W. Zhang, and G. Lim Hoe, "A Novel Static Dual Edge- Trigger Flip-flop for High-Frequency Low-Power Application," in International Symposium on Integrated Circuits, 2007, pp. 208-211.

- P. Myint Wai, F. Kangkang, G. Wang Ling, and Y. Kiat-Seng, "Power-Efficient Explicit-Pulsed Dual-Edge Triggered Sense-Amplifier Flip-Flops," in IEEE Transactions on Very Large Scale Integration (VLSI) Systems., vol. 19, pp. 1-9, 2011.

- 36. J.-I. Kim and B.-S. Kong, "Dual edge-triggered flip-flop with modified NAND keeper for high-performance VLSI," in Current Applied Physics, vol. 4, pp. 49-53, 2004.

- C. K. Teh, M. Hamada, T. Fujita, H. Hara, N. Ikumi, and Y. Oowaki, "Conditional Data Mapping Flip-Flops for Low-Power and High-Performance Systems," in IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 14, pp. 1379-1383, 2006.

- Z. Peiyi, T. K. Darwish, and M. A. Bayoumi, "High-performance and low-power conditional discharge flip-flop," in IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 12, pp. 477- 484, 2004

- K. Bai-Sun, K. Sam-Soo, and J. Young-Hyun, "Conditional-capture flip-flop for statistical power reduction," in IEEE Journal of Solid-State Circuits, vol. 36, pp. 1263-1271, 2001.

- C. Y. Kiang, "Low Power Circuits for High Performance Systems," in Final Year Project Report, Nanyang Technological University, 2010.